Open Verification Library (OVL) is a library of property checkers for digital circuit descriptions written in popular Hardware Description Languages and maintained by Accelera. The OVL checkers could be used not only in dynamic simulation, but also in formal verification and emulation. Also, the OVL-based verification technology provides the easiest way for designers to implement assertion-based verification of their design. Finally, OVL supports any HDL language (Verilog, SystemVerilog, VHDL), enabling assertion-based verification with any simulation tools.

In this webinar, we will present practical guidance on how to start using Open Verification Library (OVL) in design and verification process. We will provide various code examples to demonstrate how to efficiently use OVL for Verilog and VHDL design verification. Static formal and emulation-based verification methods using OVL will be outlined as well.

Agenda:

- Assertion-Based Verification: An Overview

- Introduction to Assertion-Based Verification with OVL

- Applying OVL – based verification on HDL designs

- Using OVL checkers in emulation/prototyping

- Formal Model checking with OVL

- Live-Demo

Essential steps to simplify VHDL testbenches with OSVVM

This Getting Started webinar focuses on the first, essential steps you need to take if you want to improve your VHDL testbench approach with OSVVM.

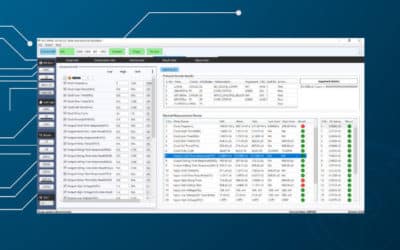

Checking AXI connections with ALINT-PRO and Riviera-PRO

AXI has become the most popular internal bus protocol with today’s FPGA and SoC FPGA designs. ALINT-PRO enables FPGA designers to extract, review and statically verify AXI bus interfaces. In addition, ALINT-PRO can assist with automatic generation of test harnesses...

embedded world 2023

From March 14 to 16, embedded world in Nuremberg will once again be open to visitors. At booth 4-548 of eVision Systems, we look forward to meeting everyone who wants to learn about our many new innovations!

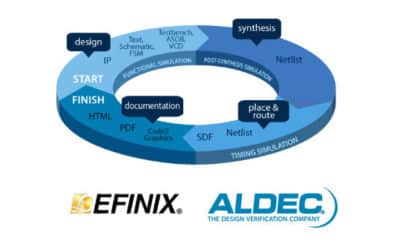

Effinix and Aldec Active-HDL promotion

Active-HDL Designer Edition Perpetual License – Request a quote! Active-HDL™ is a Windows® based, integrated FPGA Design Creation and Simulation solution for team-based environments.

SHA850A first handheld spectrum & vector network analyzer

The new analyzer is highly integrated and specially designed for field operation. The device is handy and lightweight and has many useful analysis functions integrated.

Industry’s first electrical AC DC validation solution for SD cards and eMMC devices

PGY-SSM-EV-TesterForstinning (Germany), November 23, 2022 - eVision Systems GmbH, authorized Prodigy Technovations distributor for Central Europe, announced its PGY-SSM-EV-Tester SD, eMMC AC/DC Electrical Validation Tester for electrical characterization of SD card...

What is a logic analyzer?

A logic analyzer is an electronic measurement device that captures and displays multiple signals from a digital design. It is an excellent tool for checking and debugging ICs, digital systems, circuits such as embedded systems, electronic control units, computers,...

eVision Systems GmbH announces innovative PCIeGen3 and 4 protocol analyzer from Prodigy Technovations

PGY-PCIeGen3/4-PA PCIe Protocol AnalyzerForstinning (Germany), October 09, 2022 - eVision Systems GmbH, the authorized distributor of Prodigy Technovations for Central Europe, announces the PGY-PCIeGen3/4-PA PCIe Protocol Analyzer, the 2.5, 5.0. 8.0 and 16GT/S speeds...

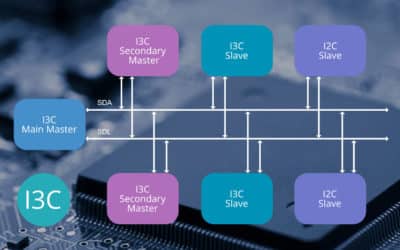

The 10 biggest problems with the development using the I3C bus system

Developers of end devices and embedded systems, especially for use in IoT (Internet of Things), automotive and industrial automation, are faced with ever-increasing demands for low power consumption, data bandwidth, and miniaturization. To meet them, the embedded...

Riviera-PRO supports OpenCPI for heterogeneous embedded computing

Aldec supports the Open Component Portability Infrastructure (OpenCPI) with the latest version of Riviera-PRO (version 2022.04).