UVM Register Model Generation

System RDL and IP-XACT Compiler

Automatically generate UVM Sequences

Advanced SoC Verification Tool

Agnisys Inc. – Automation of SOC, ASIC, FPGA and IP Specification

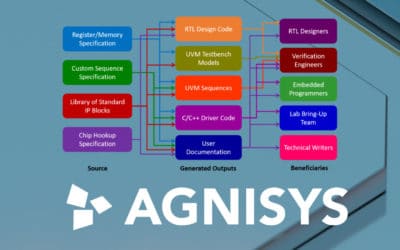

Save valuable project time and resources by automatically generating many types of design and verification files from technical specifications.

Agnisys Inc. has developed a suite of specification automation products and solutions that streamline the generation of the required design, software, verification, validation, and documentation files for semiconductor development directly from executable specifications. This saves your IP and chip development teams time and effort several times throughout a project. Whenever a specification changes for any reason, all output files are updated so that all teams remain at the same level.

Agnisys is thus a leading provider of Electronic Design Automation software for solving complex design and verification problems in system development. The products provide a common, specification-driven development flow for describing registers and sequences for System-on-Chip and IPs (Intellectual Property), enabling faster design, verification, firmware, and validation. Agnisys is headquartered in Boston, Massachusetts, and has R&D centers in the United States and India.

The methodology for faster development of better semiconductors

The dilemma between specification and design

Traditionally, there was no automated link between design specifications and the development process. The designers wrote the RTL specification by hand, the embedded systems programmers wrote the C/C++ code by hand, and the verification teams coded testbenches and tests – all based on the same specification. Natural language is inherently ambiguous, so different teams had different interpretations. Much of the project was spent fixing bugs due to inconsistencies.

Effects of specification changes

Specifications change frequently over the course of a project, and each time this happened, the development process was repeated. The changes had to be communicated to the individual teams, who interpreted them and updated their code manually. Inevitably, new inconsistencies arose, leading to tedious troubleshooting to correct the problems. The cost to the schedule and project resources was enormous.

Executable specifications save time and reduce errors

In the Agnisys methodology, many specifications can be written in executable formats from which the Agnisys tools can automatically generate design, programming, verification, validation and documentation files. Each time a specification is changed, all files are automatically regenerated to incorporate the changes. This replaces tedious manual work and ensures that all your teams are on the same page at all times.

Agnisys announces ISO 26262 and IEC 61508 qualification for entire automation process in SoC specification

Developers of safety-related electrical/electronic systems in motor vehicles can now use Agnisys solutions without additional tool qualification

Specification Automation for Designers

Requirements for various project teams and various tasks in the System-on-Chip (SoC) development process: hardware design, simulation, formal verification, firmware coding, system-level validation, and more.

A high quality standard for standards-based IP

The Standard Library of IP Generators (SLIP-G™) has proven to be very popular with users, and this is not surprising. Reuse plays a significant role in system-on-chip (SoC) development.

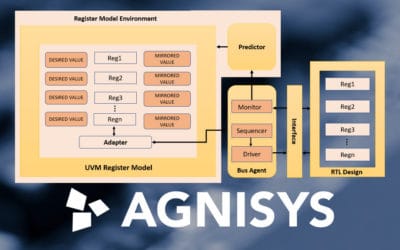

Automating the UVM Register Abstraction Layer (RAL)

This post focuses on the UVM Register Abstraction Layer (RAL), sometimes called the UVM Register Layer. Today’s large system-on-chip (SoC) designs contain many control and status registers, often accessible from embedded software or drivers as well as hardware.

Automation of IP and SoC development

Agnisys has expanded its original focus on register automation to encompass specification-driven design, verification, embedded programming, validation, and documentation of IPs and SoCs This expansion is a testament to Agnisys growth and the many challenges semiconductor development teams face.

Webinar on Embedded System Development Using Agnisys

Embedded System Development Using Agnisys This provides a path that avoids many pitfalls present in a typical flow, such as a slow process, duplicate efforts, wasteful resources, and so on.

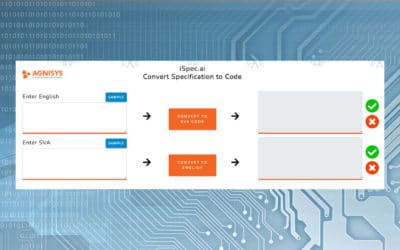

Automatically translate English description into SystemVerilog Assertions

Agnisys has developed a unique approach that uses artificial intelligence (AI) and machine learning (ML) to translate English descriptions of design intent into SystemVerilog Assertions (SVA).