Static verification

When creating VHDL code, a lot of errors can happen. These can be simple typos, syntax errors, semantic errors or structural errors.

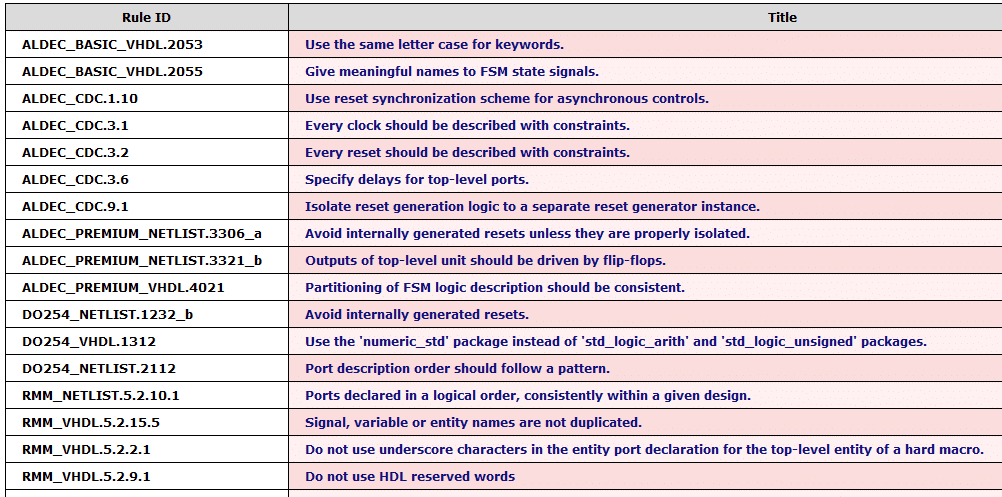

Especially errors that are not visible during the compilation of a single file can usually not be detected by the editor alone. Linting tools can be used to detect such problems in time. These also enable compliance with specially defined design rules. With Alint-Pro, ALDEC offers a linting tool for which various rule sets are available and enables cross-file checks such as CDC checks (Clock Domain Crossing).

Dynamic Verification

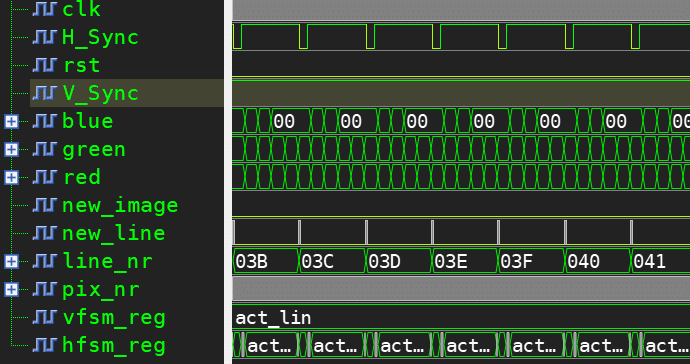

To verify the function of a hardware model (e.g. in VHDL or Verilog), it is necessary to check how the HDL model behaves in the context of the system. This can be achieved, for example, by modelling the behaviour with so-called properties, or by stimulating the HDL code. For this stimulation, one usually uses a testbench that more or less completely reproduces the behaviour of the system. Simulators such as Riviera-Pro from ALDEC can process properties and simulate abstract models of external components (e.g. SystemC models). Riviera-Pro offers extensive debugging functions and supports VHDL, Verilog, System-Verilog and SystemC.