Creating HDL Descriptions for ASIC and FPGA Designs

Whether you are working with VHDL or Verilog, you will notice that Hardware Description Languages (HDL) are different from sequential programming languages because VHDL and Verilog are parallel languages specified for modelling hardware.

Graphics or text?

This question cannot be answered easily and is also often evaluated very subjectively. In general, a graphical representation fits well with parallel languages like VHDL and Verilog. Nevertheless, innovative text editors can also provide great value, especially if they have the ability to generate graphics from the text.

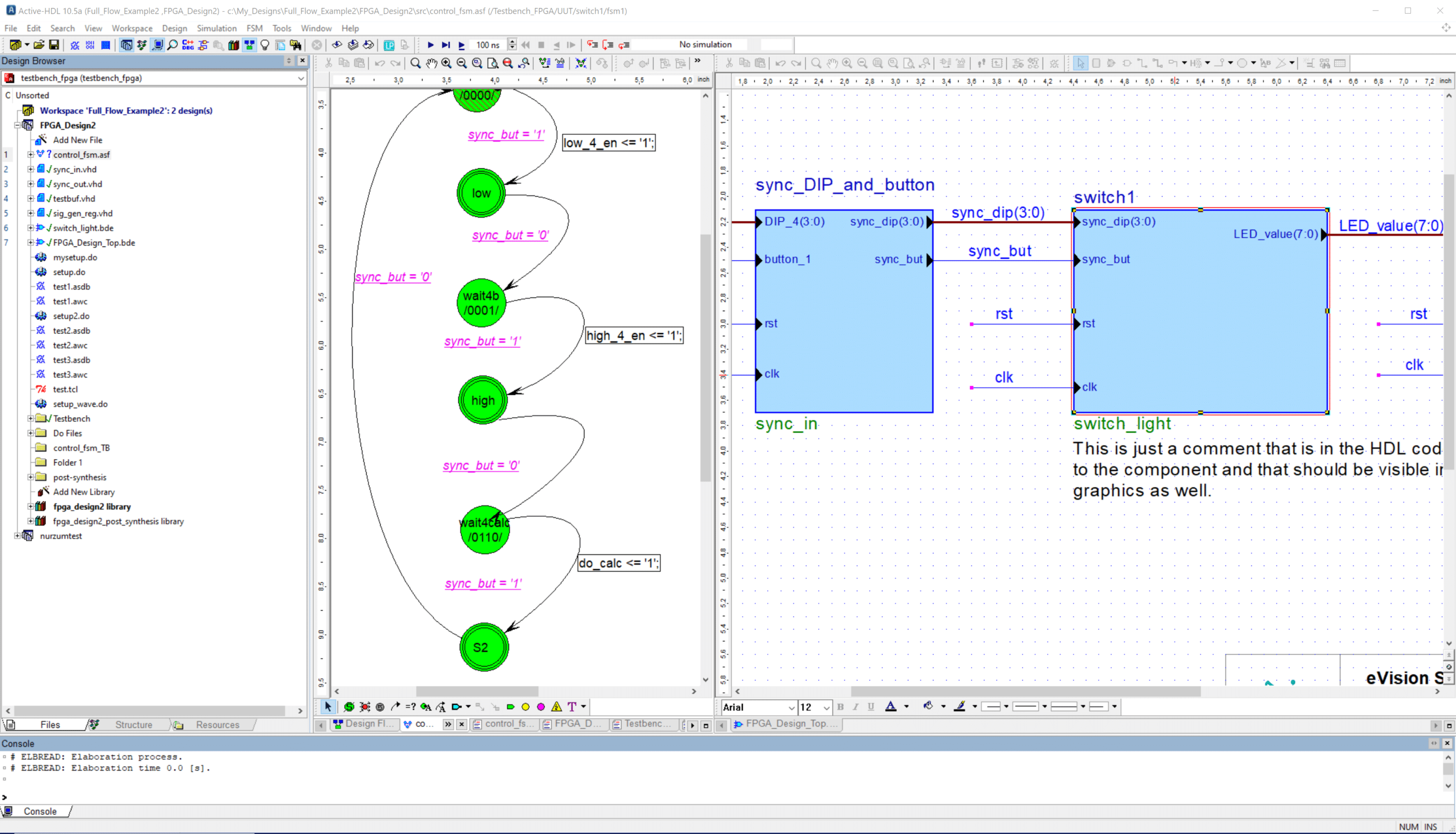

Are you looking for an integrated development environment that offers the possibility to enter block diagrams and state transition diagrams (automata) directly in a graphical editor and generate the corresponding VHDL or Verilog code automatically? Would you like to have the additional possibility to create HDL code with an integrated text editor and simulate the design directly in the same tool?

Then we recommend Active-HDL from ALDEC.