Static Design Verification

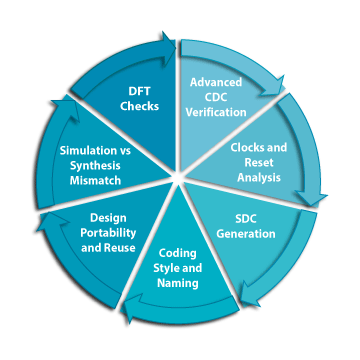

ALINT-PRO™ is a design verification solution for RTL code written in VHDL, Verilog, and SystemVerilog. It is focused on verifying coding style and naming conventions, RTL and post-synthesis simulation mismatches, smooth and optimal synthesis, correct FSM descriptions, avoiding problems on further design stages, clocks and reset tree issues, CDC, RDC, DFT, and coding for portability and reuse. The solution performs static analysis based on RTL and SDC™ source files uncovering critical design issues early in the design cycle, which in turn reduces design signoff time dramatically. Running ALINT-PRO before the RTL simulation and logic synthesis phases prevents design issues spreading into the downstream stages of design flow and reduces the number of iterations required to finish the design.

Single Framework for DRC and CDC/RDC Analysis

ALINT-PRO features a well-designed, intuitive framework, which offers features for efficient design analysis including RTL schematic viewer, FSM viewer, clocks and resets viewer, control schematics viewer, elaboration viewer, violation viewer, and special tools such as CDC viewer, RDC viewer, and CDC schematics for clock and reset domain crossings analysis.

Setting up an existing HDL design for analysis in ALINT-PRO is supported by reading external project file formats (Aldec Active-HDL, Aldec Riviera-PRO, Xilinx Vivado, Xilinx ISE, Intel Quartus), interpreting typical simulation scripts (compatibility commands like vcom, vlog, vsim, vlib) as well as traditional file lists for the batch-mode tools, and very simple GUI wizards for direct import of individual files and whole directories.

Full Chip-Level Linting vs. Unit Linting

Full chip-level linting runs the analysis of the design’s hierarchy as a whole, with particular values of generic parameters propagated from the top-level instances down to the leaf submodules, as well as applying the user-defined timing constraints. This methodology is traditional for typical HDL linting tools, and is more often utilized during signoff periods, or for types of verification that require exploring the entire design at once as an already integrated system (clock and reset checks, CDC, RDC, DFT). This methodology assumes that the whole or, at least, most of the design under test is already implemented.

Unit linting is a relatively new approach that is well combinable with a flat elaboration mode – a special kind of elaboration, which considers HDL design units independent of each other in isolation, and is using the default values of generic parameters. This processing style is highly forgiving of missing elements within designs, such as not yet implemented parts of the hierarchy. This makes unit linting most valuable both when applied to individual source files, independent of other files, and right after files have been modified by a designer. Many highly valuable rule checks are therefore enabled very early, even almost immediately following writing the code itself, thus squeezing the feedback loop for the designer from days or weeks to just a few seconds. A natural application for unit linting is integration with HDL editors, with unit linting running in the background, which is provided in the latest versions of Aldec Active-HDL™ and Riviera-PRO™, as well as some of the popular 3rd-party HDL editors.

Unit linting does not eliminate a need to use full traditional linting, as the combination of independent units may create extra issues after integration. However, systematically applying unit linting can dramatically reduce the amount of verification during signoff periods.

Checking FPGA Designs

ALINT-PRO smoothly supports running the rule checks for designs that target FPGA implementation using Xilinx, Altera, Microsemi, and Lattice technologies with minimal setup. ALINT-PRO offers the latest versions of FPGA vendor libraries, which are pre-built, installed by default, and pre-configured for advanced timing and CDC rule checks.

ALINT-PRO automates setup of hierarchical and incremental analysis flow for IP-based FPGA designs. Each IP block may be separately analyzed first, and the extracted timing constraints can be promoted and re-used for much faster higher-level design analysis. Unless the IP-block is re-configured in the original design environment, its body is only analyzed once, saving numerous amounts of time during the subsequent runs of the main FPGA design.

Batch Mode Flows

Key ALINT-PRO functions are also accessible via a rich set of TCL-based scripting commands. The scripts can be used to automate design rule checks, repetitive settings, and reports generation. The scripts can run in an interactive console shell or in fully automatic batch mode. Finally, ALINT-PRO is capable of running the most typical design entry and linting scenarios in true batch mode using a single command-line shell application call, which makes it perfectly suitable to integrate with larger regression testing scripting and continuous integration environments, such as Jenkins.

Available Rule Libraries for ALINT-PRO™

ALINT-PRO includes rule libraries based on STARC (Semiconductor Technology Academic Research Center) and RMM (Reuse Methodology Manual) design guidelines, which utilizes best practices in design development used by semiconductor companies all over the world. For safety-critical designs, Aldec delivers rule libraries based on DO-254 guidelines focused on critical issues analysis that impact design stability. For RISC-V Design Community, ALDEC offers the RISC-V rule plugin, based on the industry-proven best IP design practices and guidelines.

The main rule plugins are complemented with highly configurable Aldec Basic and Premium rule libraries, which are driven by Aldec in-house experience with FPGA and ASIC digital design, as well as include many additions recommended by existing ALINT-PRO customers, fighting against chip killer issues in industrial-scale designs. ALDEC SV plugin targets new varieties of RTL mistakes specific to SystemVerilog design subsets.

The ALDEC_CDC rule plug-in turns ALINT-PRO into a full-scale CDC and RDC Verification solution capable of complex clock and reset domain crossings analysis and handling of metastability issues in modern multi-clock and multi-reset designs. The verification strategy in ALINT-PRO is comprised of three key elements: static structural verification, design constraints setup, and dynamic functional verification. The first two steps are executed in ALINT-PRO, while dynamic checks are implemented via integration with simulators (Riviera-PRO™ , Active-HDL™, and ModelSim® are supported) based on the automatically generated testbench. This approach reveals potential metastability problems during RTL simulation, which otherwise would require lab tests to be detected. Debugging CDC and RDC issues is being achieved via rich schematic and HDE cross-probing mechanisms, as well as comprehensive reports and TCL-based API, which allows browsing through synthesis results, clocks and resets structures, detected clock and reset domain crossings, and identified synchronizers.

Features

Clock and Reset Networks Analysis

Avoiding post RTL and post Synthesis Simulation Mismatches

Verifying correctness of FSM descriptions

Graphical exploration of extracted FSMs and the indentified FSM issues

Code Portability and Reuse

Extensive CDC and RDC checks with ALDEC_CDC rule plug-in

Advanced CDC and RDC Debugging Environment

Schematic Viewer

DFT Checks

SDC™ Support