HW/SW Co-Design

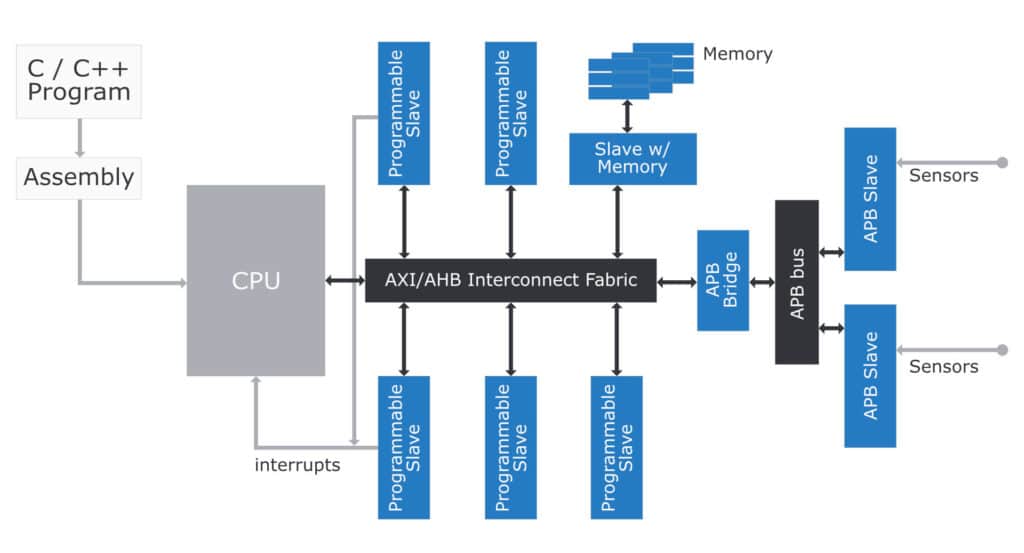

When designing System On Chip components, the definition of the hardware-software interface plays a major role. Especially for larger teams working on complex SoCs, it must be ensured that addresses are not assigned more than once and that the address assignment in the hardware matches the implementation on the software side.

In general, FPGA or ASIC-based systems consist of:

- Own HDL code

- IP blocks of the FPGA, ASIC manufacturer

- Purchased IP blocks

In addition, various software components such as:

- Low level device drivers

- Possibly an operating system

- Possibly a High-Level API (Application Programmable Interface)

- The application software

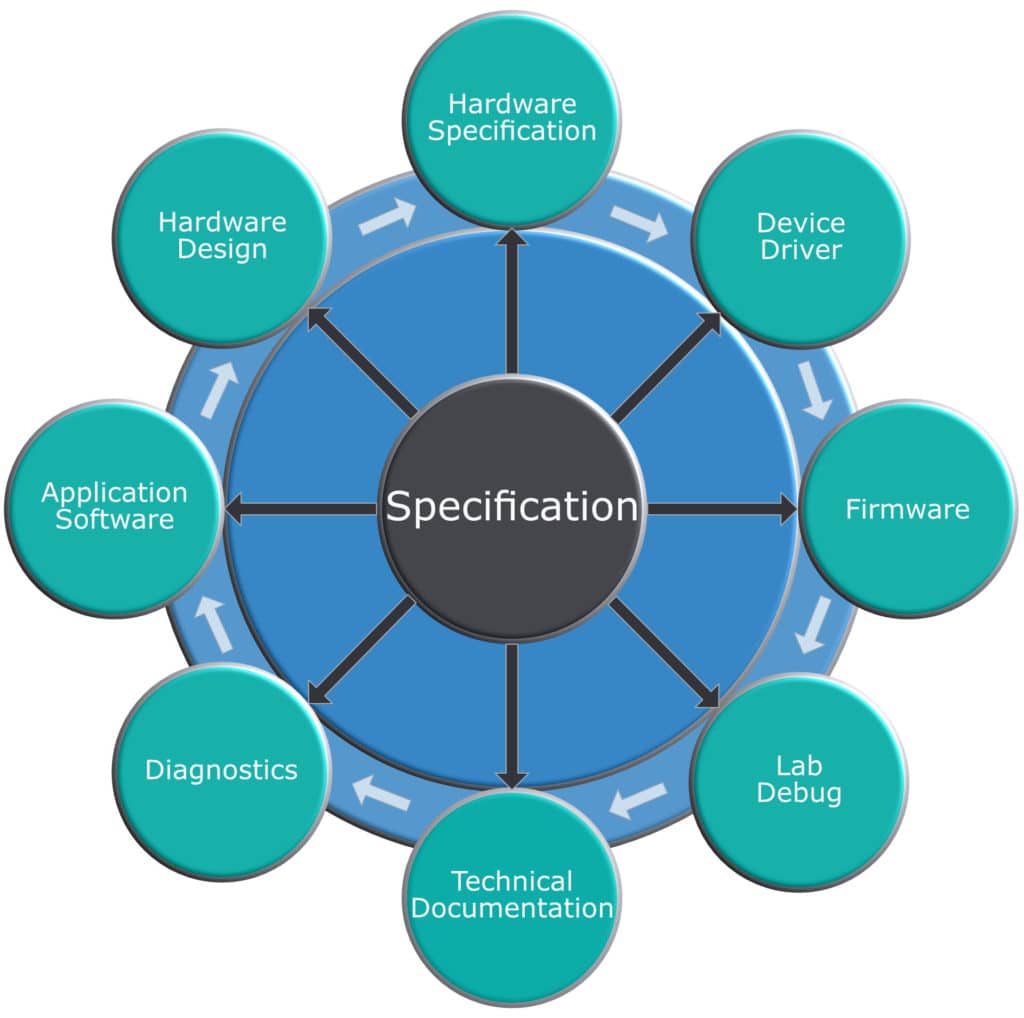

As soon as something changes in the register specifications or implementations, this impacts the various development teams. Therefore, a structured and automated development methodology regarding the description and generation of the register specification and implementation is paramount in order not to struggle with errors discovered too late or even overlooked errors in the HW/SW interface during the development process. Our partner Agnisys has developed iDesignSpec, an innovative solution to ensure that the HW/SW interface is cleanly implemented and verified. The source codes for the various steps are then generated from a central location (see graphic).

HW-SW Co-Simulation

If the interaction of hardware and software is simulated, the question arises of how a simulation environment can be set up. Especially the verification of drivers is a challenge. With the help of the QEMU bridge and the ALDEC AXI BFM, Riviera-Pro allows co-simulation between HDL Design and the open-source processor emulator QEMU.