In this webinar we present the Agnisys way of developing embedded products. This provides a path that avoids many pitfalls present in a typical flow, such as a slow process, duplicate efforts, wasteful resources, and so on.

Generate code directly from specification using best-in-class Agnisys products and innovative tool flow. Agnisys flow involves the use of IDesignSpec™, which starts by defining the Hardware-Software Interface (HSI) of the embedded system, followed by defining the user application logic using DVinsight™, customising standard IPs with SLIP-G™, and connecting all the components using SoC Enterprise™, and getting a jump-start on the software stack using ISequenceSpec™. Create automated UVM-based verification environments using Specta-AV™ and tests using ARV™ and ASVV™.

There’s no more wasted time, no more wasteful resources, and no more sub-optimal code. Agnisys brings a new way of creating embedded designs that just works. In the webinar we will go through a typical embedded system development using this new Agnisys way.

Benefits of Using Agnisys Flow:

- The suite of Agnisys tools help you automate the Embedded System development process

- Provide real value to architects, designers, verification engineers, software developers, technical writers, and chip testers

- Focus is on User Application Logic and not the plumbing (connectivity)

- Agnisys Flow cuts down the time it takes to develop Embedded Systems

- Makes your teams more productive and efficient

- Produces high quality, repeatable result

- This saves time and money and improves overall quality

- All tools are available independently or as a complete flow

Learning Outcomes:

- How to reduce development time by 30%

- How to use a development methodology that is highly efficient

- What steps can be automated such that minimum effort and resources are required to develop the embedded system

Recent Agnisys posts

Specification Automation for Designers

Requirements for various project teams and various tasks in the System-on-Chip (SoC) development process: hardware design, simulation, formal verification, firmware coding, system-level validation, and more.

A high quality standard for standards-based IP

The Standard Library of IP Generators (SLIP-G™) has proven to be very popular with users, and this is not surprising. Reuse plays a significant role in system-on-chip (SoC) development.

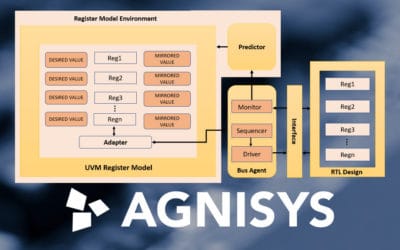

Automating the UVM Register Abstraction Layer (RAL)

This post focuses on the UVM Register Abstraction Layer (RAL), sometimes called the UVM Register Layer. Today’s large system-on-chip (SoC) designs contain many control and status registers, often accessible from embedded software or drivers as well as hardware.

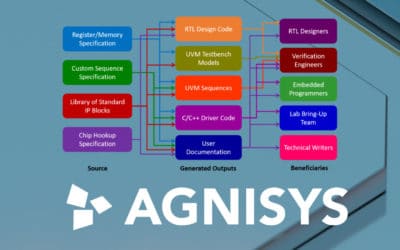

Automation of IP and SoC development

Agnisys has expanded its original focus on register automation to encompass specification-driven design, verification, embedded programming, validation, and documentation of IPs and SoCs This expansion is a testament to Agnisys growth and the many challenges semiconductor development teams face.

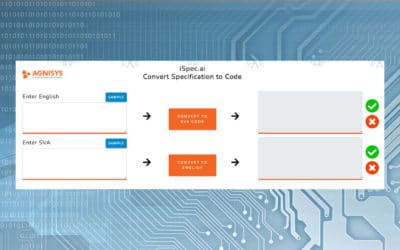

Automatically translate English description into SystemVerilog Assertions

Agnisys has developed a unique approach that uses artificial intelligence (AI) and machine learning (ML) to translate English descriptions of design intent into SystemVerilog Assertions (SVA).