Aldec’s prototyping solution for Microchip™ RTAX-S/SL and RTSX-SU devices utilizes reprogrammable flash-based ProASIC3E FPGA’s (both the RTAX/RTSX and ProASIC3E device families belong to Microchip). The RTAX-S/SL and RTSX-SU prototyping package include a prototyping adaptor board that maps the footprint of the ProASIC3E device to the footprint of the RTAX-S/SL and RTSX-SU device (e.g. CQ208, CQ256, CQ352, CG624). . Support is also available for the larger CG1272 packages. After soldering the adaptor to the PCB, the ProASIC3E device can be reprogrammed through the JTAG interface connector.

RTAX/RTSX Netlist Converter

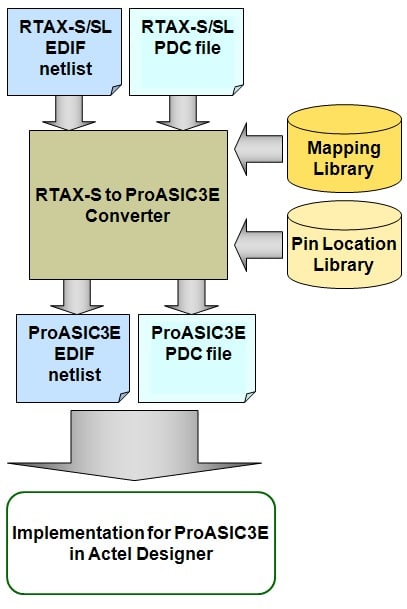

The RTAX / RTSX EDIF and PDC / PIN converter combines two functions to support Aldec RTAX prototyping – it offers EDIFs netlist conversion and PDC / PIN constraints file remapping for the two families RTAX-S / SL and RTSX- SU / S, SX-A. RTAX/RTSX EDIF and PDC/PIN Converter perform automatic conversion of the RTAX-S/SL and RTSX-SU/S, SX-A EDIFs netlists to ProASIC3/E EDIF netlist, which means replacement of the PLL and memory primitives has to be done, with consideration of the limitations caused by the differences between RTAX-S/SL, RTSX-SU/S, SX-A and ProASIC3/E technologies.

RTAX / RTSX-Adapterkarten

Aldec and Microchip have partnered to offer a new, innovative, reprogrammable prototyping solution for the Microsemi RTAX-S / S and RTSX-SU space system designs. Unlike the traditional OTP (One Time Programmable) anti-fuse space-qualified FPGAs, the Aldec prototype adaptor uses flash-based, Microchip ProASIC®3E FPGA technology, for design prototype re-programmability.

Top Features

- Power supply and footprint compatibility

- Automated Device Netlist Converter:

Memory Conversion - Physical Design Constraint (PDC) file conversion