The Standard Library of IP Generators (SLIP-G™) has proven to be very popular with users, and this is not surprising. Reuse plays a big role in system-on-chip (SoC) development because no team can afford to design and verify a billion or more gates from scratch. There is no prospect of reversing this trend, so we are seeing a lot of interest in many design and verification IP’s, especially those that implement industry standards. Agnisys has worked hard to support users and expand their IP titles.

It is important to emphasize that Agnisys provides a library of IP generators and not fixed IP blocks. This is essential given the variety of applications that use SoCs and the mix of technologies (FPGA, ASIC, and fully custom) used to build these complex chips. Each chip project has its own requirements for its IP blocks, with feature selection often resulting from tradeoffs between speed, area and power. Only a generation-driven solution can satisfy these needs. Options and customizations must be built into the generators so that users are not tempted to manually edit the register transfer level (RTL) design files.

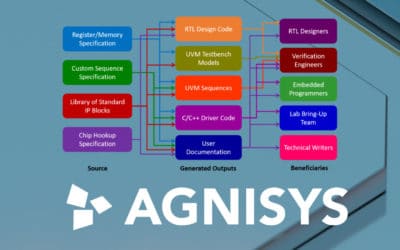

SLIP-G generates the IP RTL code integrated into the entire SoC and the user’s design parts. Agnisys SoC Enterprise™ (SoC-E) automates this process and works seamlessly with SLIP-G. However, Agnisys offers much more than just design. For each IP, SLIP-G also generates Universal Verification Methodology (UVM) models to help create the verification testbench, as well as a set of programming sequences to initialize and configure the selected block’s registers. You will also generate C/C++ sequence APIs (Application Programming Interfaces) for developing firmware and drivers that access the IP block.

Finally, Agnisys produces detailed documentation to be made available to the SoC’s end users. SLIP-G helps every group involved in SoC development: hardware designers, verification team, lab bring-up/validation engineers, and technical writers. Agnisys even provides output files that can be used in the development of automated test equipment (ATE) programs for production chips in the manufacturing process. In doing so, Agnisys sets a high standard for the delivery of standards-based intellectual property, and while the library is expanding, Agnisys continues to provide the same quality and flexibility for all new titles.

SLIP-G was introduced last year with four IP blocks: General Purpose Input/Output (GPIO), I2C, Timer and Programmable Interrupt Controller (PIC). These have many configuration and customization options to meet the needs of a diverse user base. So far this year, four more entries have been added to the library: Direct Memory Access (DMA), Serial Peripheral Interface (SPI), Pulse Width Modulation (PWM) and Advanced Encryption Standard (AES). These are numerous options available when generating these blocks with SLIP-G.

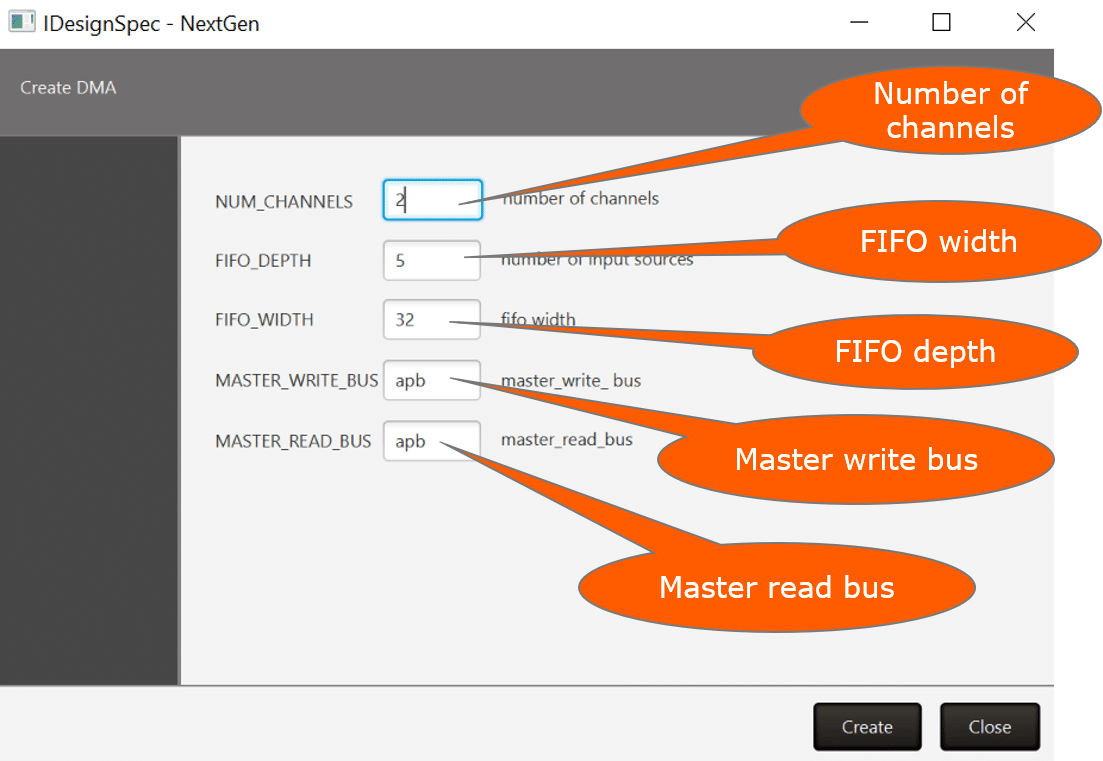

The DMA enables SoC subsystems to access the system’s main memory independently of the central processing unit (CPU). This frees up the CPU for important calculations instead of just moving data around. The DMA-IP has two masters and four channels with integrated round-robin arbitration across channels. It can handle transfers from memory to peripheral, peripheral to memory, peripheral to peripheral, and memory to memory. It offers configurable channels and includes an interrupt controller for status and diagnostics.

SPI is a synchronous serial interface specification used for short distance communication. The CPU uses the SPI registers to program the IP block to initiate a transaction. The data length, the command length and the address length are all configurable. The options also include whether interrupts are to be generated with an enabling or a mask. PWM is a method of controlling analogue devices with a digital output by modulating an output signal. It is one of the primary means by which processors control analogue devices such as variable-speed motors, dimmable lights, actuators, and speakers. The PWM IP block offers the following features:

- Customizable number of PWM output signals

- Customizable number of external sources

- A prescaler register for generating the PWM signals with a slower clock than the system clock

- Configurable widths for control registers

- Standard APIs to program the block

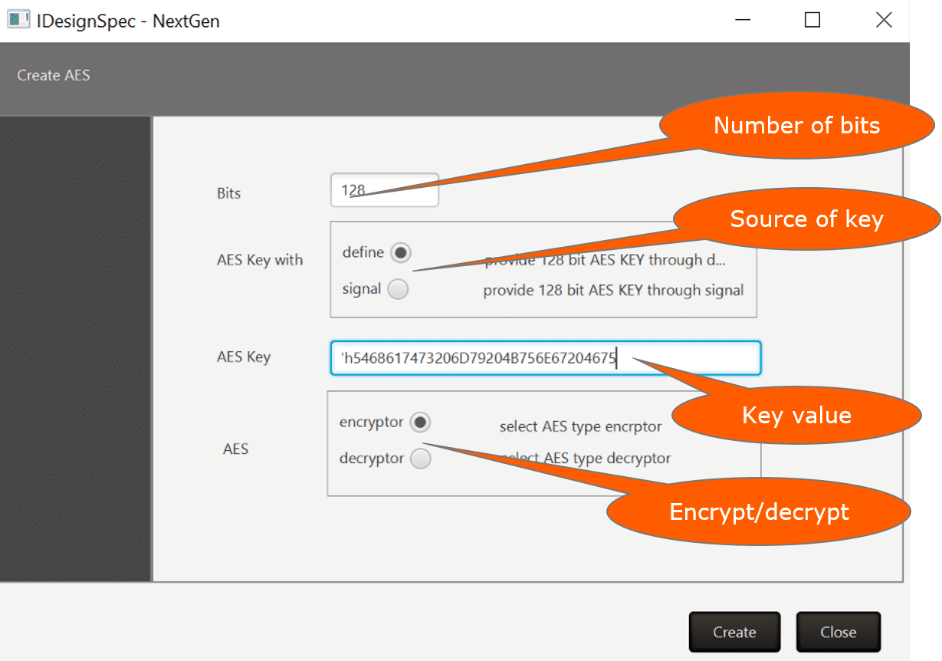

AES is a standard for encrypting and decrypting sensitive electronic data that is applicable to both hardware and software. It can handle three different key sizes (128, 192 and 256 bits) and supports a 128-bit block size. We support 128-bit keys and 128-bit blocks. During IP generation, the user can choose whether the key value should be supplied to the block via an input signal or defined in the RTL code. In the latter case, the user specifies the key value. Other customization options include whether the block is configured for encryption or decryption.

SLIP-G also allows for user customization, such as adding fields to existing registers, adding additional registers, adding logic to the IP, and setting up dependencies of events within the IP block. Agnisys is constantly adding new generation options based on user requests and continuing to expand the library. Agnisys has also recently joined the Mobile Industry Processor Interface (MIPI) Alliance and is considering the development of MIPI-based IP. Their standards extend to camera, displays, power management and more, so Agnisys believes there will be significant interest among the user base.

Please let us know if you have suggestions for new IP titles or new features for existing blocks. Agnisys is proud of its SLIP-G family and its unique support for hardware reuse, verification data reuse, programming sequence reuse, and documentation reuse. Agnisys is excited to help you develop ever larger SoCs and do so without exploding the size of your team or your project timelines.

Specification Automation for Designers

Requirements for various project teams and various tasks in the System-on-Chip (SoC) development process: hardware design, simulation, formal verification, firmware coding, system-level validation, and more.

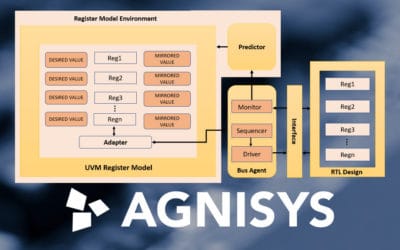

Automating the UVM Register Abstraction Layer (RAL)

This post focuses on the UVM Register Abstraction Layer (RAL), sometimes called the UVM Register Layer. Today’s large system-on-chip (SoC) designs contain many control and status registers, often accessible from embedded software or drivers as well as hardware.

Automation of IP and SoC development

Agnisys has expanded its original focus on register automation to encompass specification-driven design, verification, embedded programming, validation, and documentation of IPs and SoCs This expansion is a testament to Agnisys growth and the many challenges semiconductor development teams face.

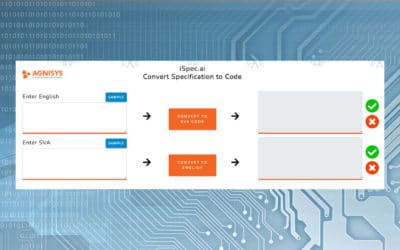

Automatically translate English description into SystemVerilog Assertions

Agnisys has developed a unique approach that uses artificial intelligence (AI) and machine learning (ML) to translate English descriptions of design intent into SystemVerilog Assertions (SVA).